NPTEL Digital Circuits Week 4 Assignment Answers 2024

1. Which of the following property is WRONG?

A) A XORO= A’

B) A XOR 1 = A*

C) A XOR A = 0

D) A XOR A’ = 1

Answer :- For Answer Click Here

2. Minimum number of NAND gates are required to design a 2-input XOR gate is_________________.

A) 3

B) 4

C) 5

D) 6

Answer :- For Answer Click Here

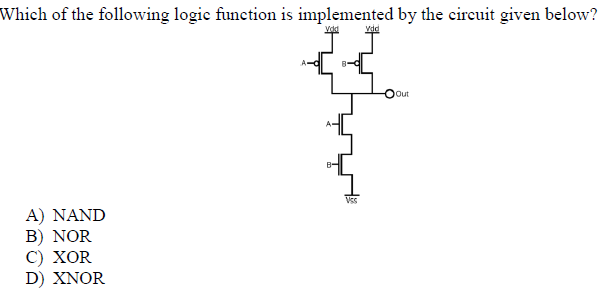

3.

Answer :-

4. How many transistors are required to design a CMOS 2-input NOR gate?

A) 2 PMOS and 1 NMOS transistors

B) 1 PMOS and 2 NMOS transistors

C) 3 PMOS transistors

D) 2 PMOS and 2 NMOS transistors

Answer :-

5. What is a hazard in digital circuits?

A) An error in the physical layout of the circuit

B) A temporary fluctuation in output due to changes in input

C) A permanent fault in the circuit

D) A delay in the clock signal

Answer :-

6. In digital circuits, what type of hazard occurs when a single input change causes multiple changes in output before settling?

A) Static-1 hazard

B) Static-0 hazard

C) Dynamic hazard

D) Glitch hazard

Answer :- For Answer Click Here

7. A static-0 hazard in a digital circuit occurs when:

A) The output should remain 0, but temporarily goes to 1

B) The output should remain 1, but temporarily goes to 0

C) The output oscillates between 0 and 1

D) The output remains at a constant 0

Answer :-

8. Which of the following options correctly represents the SUM and CARRY outputs for a half adder?

A) SUM = A XOR B, CARRY = A.B

B) SUM = A XNOR B, CARRY = A.B

C) SUM = A XOR B, CARRY = A+B

D) SUM = A.B, CARRY = A XOR B

Answer :-

9. What is the primary difference between a half adder and a full adder?

A) A half adder can add two bits while a full adder can add three bits including the carry.

B) A half adder can subtract two bits while a full adder can add two bits.

C) A half adder can add three bits while a full adder can add two bits including the carry.

D) A half adder can multiply two bits while a full adder can add two bits.

Answer :- For Answer Click Here

10. How many half adders are required to construct a full adder?

A) 1

B) 2

C) 3

D) 4

Answer :-

11. When the set of input data to an even parity generator is 01111, the output will be

A) 1

B) 0

C) Don’t care

D) Depends on the previous input

Answer :-

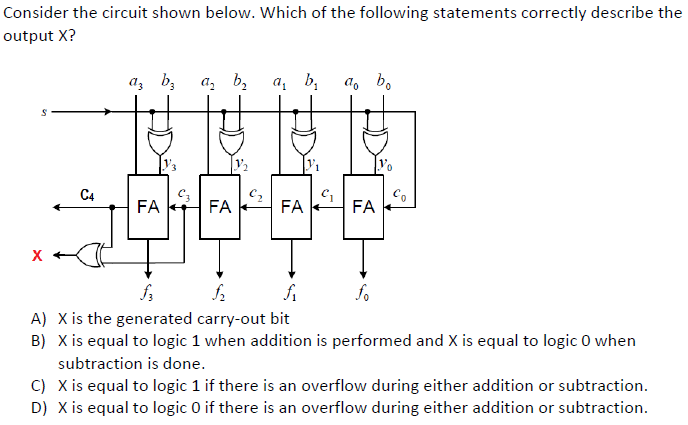

12.

Answer :- For Answer Click Here

13. The product term to be included to remove possible static hazard for the function f(Y,W,X)=WX + W’Y’ is

A) WY’

B) XY

c) W’X’

D) XY

Answer :-

14. Which of the following statement if FALSE?

A) Parity checking circuits are used for error dectection and correction

B) Parity generator circuit generates the parity bit before transmitting.

C) Parity checker circuits checks the parity at the reciever

D) Even parity checker output logic 1 when input contains even number of logic 1s

Answer :-

15. How many minimum number of transistors required to design a CMOS inverter?

A) 1 PMOS and 1 NMOS

B) 2 PMOS and 1 NMOS

C) 2 NMOS

D) 2 PMOS

Answer :- For Answer Click Here